|

The

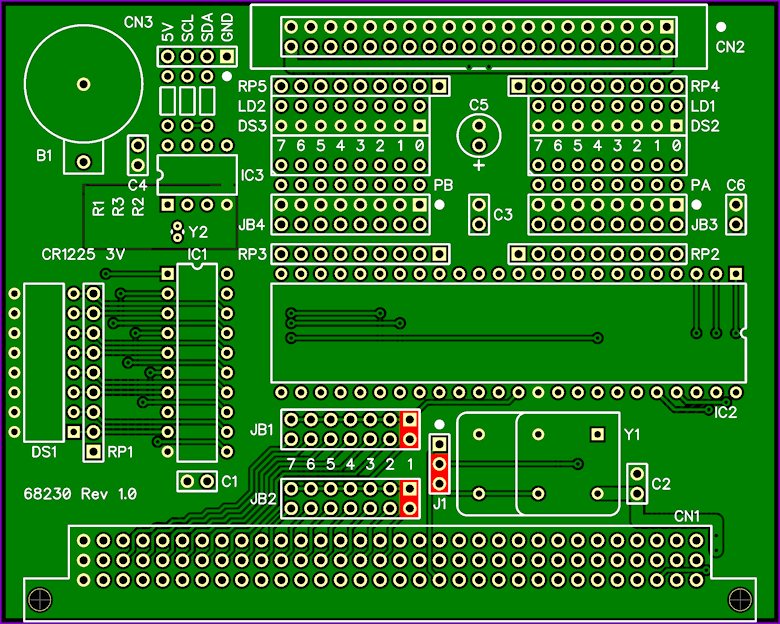

68230 Board |

| Jumpers |

| |

|

Default settings: |

place Jumpers as

shown in RED below |

|

|

| |

|

J1 CLK - Timer

Clock |

|

|

|

This Jumper

determines how the 68230 timer is clocked. The maximum

clock frequency for the timer is 10MHz and so the

dedicated clock option MUST be selected if the system

clock is greater than 10MHz. |

|

|

|

J1 pins 1-2 short

- system clock |

|

J1 pins 2-3 short

- dedicated timer clock |

|

|

|

The dedicated

timer clock frequency by default is 10MHz - to change

this frequency swap out the on board oscillator

(Y1) for a different frequency part. |

|

|

|

JB1 IACK -

Interrupt Acknowledge |

| |

|

This Jumper Block

setting must match the chosen JB2 setting. |

| |

|

JB2 IRQ -

Interrupt Priority |

| |

|

This Jumper Block

sets the timer interrupt priority (1=low, 6=high, 7=non

maskable). |

| |

| |